# PCCP

**Physical Chemistry Chemical Physics**

www.rsc.org/pccp

Volume 13 | Number 32 | 28 August 2011 | Pages 14261-14800

ISSN 1463-9076

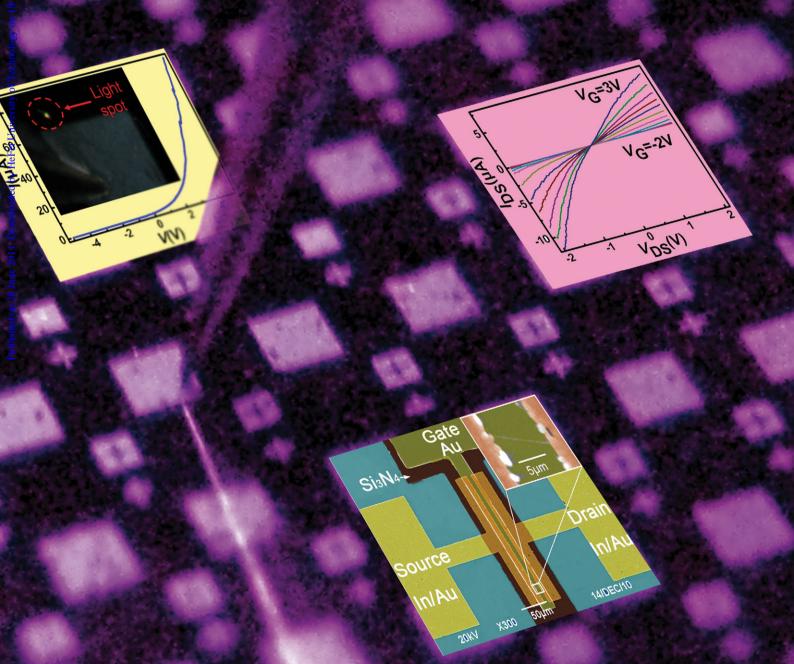

#### COVER ARTICLE

Jie *et al.* Tuning the electrical transport properties of n-type CdS nanowires *via* Ga doping and their nano-optoelectronic applications

HOT ARTICLE Fransson and Galperin Spin seebeck coefficient of a molecular spin pump Cite this: Phys. Chem. Chem. Phys., 2011, 13, 14663-14667

### PAPER

## Tuning the electrical transport properties of n-type CdS nanowires *via* Ga doping and their nano-optoelectronic applications

Jiajun Cai,<sup>a</sup> Jiansheng Jie,<sup>\*a</sup> Peng Jiang,<sup>a</sup> Di Wu,<sup>b</sup> Chao Xie,<sup>a</sup> Chunyan Wu,<sup>a</sup> Zhi Wang,<sup>a</sup> Yongqiang Yu,<sup>ab</sup> Li Wang,<sup>a</sup> Xiwei Zhang,<sup>a</sup> Qiang Peng<sup>a</sup> and Yang Jiang<sup>b</sup>

Received 8th April 2011, Accepted 19th May 2011 DOI: 10.1039/c1cp21104h

Gallium-doped n-type CdS nanowires (NWs) were successfully synthesized *via* a thermal evaporation method. The conductivities of the CdS NWs were dramatically improved by nearly nine orders of magnitude after Ga doping, and could be further tuned over a wide range by adjusting the doping level. High-performance metal-insulator-semiconductor field-effect transistors (MISFETs) were constructed based on the single CdS : Ga NW with high- $\kappa$  Si<sub>3</sub>N<sub>4</sub> dielectrics and top-gate geometries. In contrast to back-gate FETs, the MISFETs revealed a substantial improvement in device performance. Nano-light emitting diodes (nanoLEDs) were fabricated from the CdS : Ga NWs by using a n-NW/p<sup>+</sup>-Si substrate hybrid device structure. The nanoLEDs showed a bright yellow emission at a low forward bias. It is expected that the Ga-doped CdS NWs with controlled electrical transport properties will have important applications in nano-optoelectronic devices.

#### I. Introduction

CdS is an important II–VI semiconductor, with a wide direct band-gap of 2.42 eV at room temperature. It has attracted increasing interest owing to its unique electrical and optoelectronic properties. In the past decade, many efforts have been made to fabricate CdS nanostructures and further exploit their potential applications in new-generation nanoelectronics and nanooptoelectronics.<sup>1,2</sup> A variety of nanodevices, including metal– oxide–semiconductor field-effect transistors (MOSFETs),<sup>3–5</sup> optoelectronic switches,<sup>6,7</sup> sensors,<sup>8,9</sup> waveguides,<sup>10,11</sup> electrooptic modulators,<sup>12</sup> light-emitting diodes (LEDs),<sup>13</sup> and lasers *etc.*, have been actualized based on CdS nanostructures.

Doping is vital to the use of the semiconductor nanostructures in electronic and optoelectronic devices. Through appropriate n- and p-type doping, the electrical transport properties of the nanostructures could be efficiently tuned, facilitating the device construction and thereby promoting their practical applications. Therefore, it has been an urgent task in nanodevice research to survey, both theoretically and experimentally, the capability for achieving efficient doping in semiconductor nanostructures. As for CdS nanostructures, they are highly insulating, in the case of those without doping, due to the high crystal quality and the little amount of nonstoichiometric defects. Although the growth and optical properties of CdS nanostructures have been intensively studied over the past decade, <sup>14,15</sup> controlled doping of them is seldom reported and remains a challenging issue.<sup>16</sup> On the other hand, the applications of CdS nanostructures with controlled doping in high-performance nanoelectronic and nano-optoelectronic devices needs to be further exploited.

Herein, we demonstrate efficient n-type doping in CdS nanowires (NWs) by using gallium (Ga) as the donor element *via* thermal evaporation. The conductivities of the CdS NWs are dramatically enhanced through Ga doping and could be rationally tuned over a wide range by adjusting the doping level. High-performance nanoFETs and nanoLEDs are constructed based on the Ga-doped CdS NWs, indicating promising applications of the doped CdS nanostructures in future nanoelectronics and nano-optoelectronics.

#### II. Experimental details

The synthesis of the Ga-doped CdS NWs was conducted in a horizontal tube furnace *via* a simple thermal evaporation method. A similar method has been used for the synthesis of chlorine-doped CdS NWs and indium-doped CdSe NWs in our previous works.<sup>7,17</sup> In this experiment, a mixed powder of CdS (Aldrich 99.99%), Ga, and Ga<sub>2</sub>O<sub>3</sub> (0.5 g) was used as the evaporation source and placed at the center region of the furnace. The molar ratio of Ga: Ga<sub>2</sub>O<sub>3</sub> in the evaporation

<sup>&</sup>lt;sup>a</sup> School of Electronic Science and Applied Physics,

Hefei University of Technology, Hefei Anhui 230009, P. R. China. E-mail: jsjie@hfut.edu.cn

<sup>&</sup>lt;sup>b</sup> School of Materials Science and Engineering, Hefei University of Technology, Hefei Anhui 230009, P. R. China

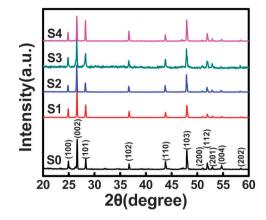

**Fig. 1** XRD patterns of both the intrinsic CdS NWs (S0) and the CdS : Ga NWs with increasing doping levels from S1 to S4.

source is 4:1, allowing the generation of Ga vapor *via* the following reactions:

$$4Ga(l) + Ga_2O_3(s) \rightarrow 3Ga_2O(g) \tag{1}$$

$Ga_2O(g) + H_2(g) \rightarrow 2Ga(g) + H_2O(g)$ (2)

It is noted that our primary attempt to use the element Ga as the n-type dopant was demonstrated to be unsuccessful since the element Ga has a very high boiling point. Si substrates coated with 10 nm Au catalyst were placed downstream, ~10 cm from the evaporation source. During the experiments, a constant H<sub>2</sub> (5% in Ar) gas flow of 60 sccm was fed and the pressure in the tube was adjusted to 200 Torr. The evaporation source was heated to 880 °C and maintained at that temperature for 2 h. In this work, four samples with varied Ga doping levels were synthesized and marked as S1, S2, S3, and S4, corresponding to the increased Ga and Ga<sub>2</sub>O<sub>3</sub> mixture to CdS mass ratio of 1%, 2%, 4%, 8%, respectively. Undoped CdS NWs were also synthesized under the same conditions, except for the use of the Ga dopant, for comparison and marked as S0.

The structures and morphologies of the as-synthesized products were characterized by X-ray diffraction (XRD, Rigaku D/Max- $\gamma$  B, with Cu-K $\alpha$  radiation), field-emission scanning electron microscopy (FESEM, Philips XL 30 FEG), and high-resolution transmission electron microscopy (HRTEM, JEOL-2010). The compositions of the products were detected by energy-dispersive X-ray spectroscopy (EDX, attached to the SEM) and X-ray photoelectron spectroscopy (XPS, VGESCALAB MKII). Room-temperature photoluminescence (PL) spectra were measured using a 325 nm He–Cd laser as the excitation source (LABRAM-HR).

To assess the electrical transport properties of the CdS: Ga NWs, two types of FETs, including the back-gate MOSFETs and the top-gate metal-insulator-semiconductor FETs (MISFETs), were constructed based on the individual CdS NWs. As for the former, the as-synthesized CdS NWs were first dispersed on a SiO<sub>2</sub> (300 nm)/p<sup>+</sup>-Si substrate, followed by photolithography and lift-off processes to define In (200 nm)/Au (20 nm) source and drain electrodes on the NWs. The degenerately doped Si substrate then served as the global back gate. To fabricate the top-gate MISFETs, a thin layer of Si<sub>3</sub>N<sub>4</sub>

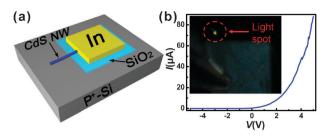

(100 nm) gate dielectric was deposited by magnetron sputtering, and then an Au (40 nm) gate electrode was fabricated *via* electron beam evaporation. To construct the nanoLEDs, a hybrid device structure that consisted of the n-CdS NW and the  $p^+$ -Si substrate was used (Fig. 6a). The SiO<sub>2</sub>/ $p^+$ -Si substrate was first etched with dilute HF (5%) solution to obtain the square SiO<sub>2</sub> insulator islands on the  $p^+$ -Si substrate, and then the CdS : Ga NWs were dispersed on the substrate. P–n junctions were formed at the regions where the NWs contacted with the  $p^+$ -Si substrate. Subsequently, In electrodes were formed on the SiO<sub>2</sub> insulator pads, covering the other ends of the NWs. All of the electrical measurements were conducted at room temperature in the dark by using a semiconductor characterization system (Keithley 4200-SCS).

#### III. Results and discussion

Fig. 1 depicts the XRD patterns of the samples, in which all of the diffraction peaks could be assigned to wurtzite CdS (JCPDS 41-1049) and no impurity peaks were observed, indicating the high phase purity of the products. In addition, the diffraction peaks of the Ga-doped CdS NWs do not show obvious peak broadening or peak shift compared with the undoped CdS NWs, implying that the doping has little influence on the crystal quality of the NWs.

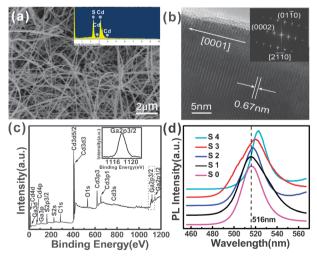

Fig. 2(a) shows a typical SEM image of the CdS : Ga NWs. The NW surfaces are clean and smooth and free of visible particles and impurities, except for the existence of Au catalyst tips. The NWs have diameters in the range of 50–200 nm and lengths from several tens of micrometres up to hundreds of micrometres. The inset in Fig. 2(a) depicts the EDX spectrum of the CdS : Ga NWs, indicating that the product is composed of Cd and S elements with a molar ratio of  $\sim 48 : 52$ . From the HRTEM image and the corresponding fast Fourier transform (FFT) pattern (Fig. 2b), it is seen that the NWs have single

**Fig. 2** (a) A typical SEM image of the CdS: Ga NWs. The inset shows the EDX spectrum. (b) A typical HRTEM image of the CdS: Ga NWs. The inset shows the corresponding FFT pattern. (c) An XPS spectrum of the CdS: Ga NWs. The inset shows the enlarged Ga 2p3/2 peak. (d) Room-temperature PL spectra of both the Ga-doped and undoped CdS NWs. The PL spectra were normalized and shifted upwards for comparison.

crystal wurtzite structures with [0001] growth orientation. XPS measurements were performed to further detect the compositions of the CdS: Ga NWs (sample S3), as shown in Fig. 2c. In addition to the Cd and S peaks, a peak at 1118 eV that corresponds to the Ga2p3/2 core level has appeared, revealing the successful incorporation of Ga in the CdS NWs. The overall content of Ga in this sample is estimated to be  $\sim 1.9$  at.%. We note that a evident red-shift of the emission bands is observed in the PL spectra of the samples (Fig. 2d). The emission band of the undoped CdS NWs (S0) is centered at 516 nm, which corresponds to the near band-edge (NBE) emission of CdS, while the bands shift remarkably to longer wavelengths of 516.1 nm, 517.5 nm, 519.5 nm, and 522.8 nm for S1, S2, S3, and S4, respectively. The red-shift of the emission bands reflects the narrowing of the CdS NW band-gap, which is caused by the broadening of the conduction band due to the introduction of a Ga donor level.<sup>18</sup> Therefore, the PL spectra also provide clear evidence for the successful Ga doping in the CdS NWs.

Fig. 3a shows the typical I-V curves of the Ga-doped CdS NWs measured by a two-probe method. The linear shape of the I-V curves indicates the ideal ohmic contact of the In electrodes with the NWs. We note that the conductance of the CdS : Ga NWs is dramatically increased compared with the undoped one (inset in Fig. 3a). The resistance of the undoped

0.05

0.00

-0.05

2

S 0

4-2024 V<sub>DS</sub>(V)

S 2

**S**4

4

(Pd)Sd)

0

$V_{\text{DS}}(V)$

**S**3

🕅 S 1

S 1 S 2

**S** 3

S4

-2

🕅 S 0

(a)10

/DS(µA)

5

0

-5

-10

20

15

10

5

(b)25

Number of NWs

-4

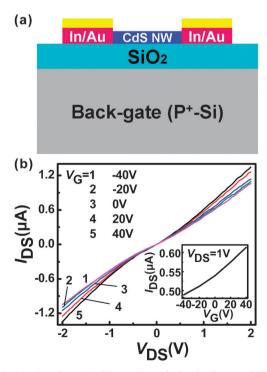

Fig. 4a shows a schematic illustration of the back-gate MOSFET based on the individual CdS: Ga NWs. From the typical gate-dependent source–drain current ( $I_{DS}$ ) versus source–drain voltage ( $V_{DS}$ ) curves of the CdS: Ga NW (sample S3) (Fig. 4b), it is seen that the conductance of the NW increases (decreases) consistently with the increasing (decreasing) gate voltage ( $V_G$ ), revealing the n-type nature of the CdS: Ga NW. This result is consistent with the anticipation that excess electrons will be generated when the Cd<sup>2+</sup> ions are substituted by the Ga<sup>3+</sup> ions. The field-effect electron mobility ( $\mu_e$ ) of the CdS: Ga NW could be estimated to be ~2.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> based on the equation:<sup>19</sup>

CdS NW is as high as  $2.5 \times 10^7$  MΩ, while it decreases to

$$\mu_{\rm e} = Lg_{\rm m} \ln(4h/d)/2\pi\varepsilon\varepsilon_{\rm SiO_2} V_{\rm DS}$$

(3)

where  $g_{\rm m} = 2.3$  nS represents the transconductance of the nanoFET and can be deduced from the slope of the  $I_{\rm DS}-V_{\rm G}$

Fig. 3 (a) Typical I-V curves of the CdS NWs with varied doping levels in the dark. The inset shows the I-V curve of an undoped CdS NW for comparison. (b) A conductivity histogram for the samples. 30 NWs each for S0, S1, S2 S3 and S4 were measured in dark.

<sup>10<sup>-7</sup></sup> 10<sup>-6</sup> 10<sup>-3</sup> 10<sup>-2</sup> 10<sup>-1</sup> 10<sup>0</sup> 10<sup>1</sup> 10<sup>2</sup> 10<sup>3</sup> Conductivity (S cm<sup>-1</sup>)

**Fig. 4** (a) A schematic illustration of the back-gate CdS NW MOSFET. (b)  $I_{\rm DS}-V_{\rm DS}$  curves of the CdS: Ga NW (S3) measured at varied  $V_{\rm G}$ .  $V_{\rm G}$  increases from -40 to 40 V in steps of +20 V. The inset shows the  $I_{\rm DS}-V_{\rm G}$  curve at  $V_{\rm DS} = +1$  V.

curve in the linear region (inset in Fig. 4b) according to the relationship of  $g_m = dI_{DS}/dV_G$ . *L*, *h*, *d*, and  $\varepsilon_{SiO_2}$  represent the NW channel length (~8 µm), SiO\_2 dielectric layer thickness (300 nm), NW diameter (~100 nm), and the SiO\_2 dielectric constant (3.9), respectively. Although the back-gate CdS : Ga NW FET exhibits an obvious gating effect, its overall device performance is still very poor, such as the large operation voltage, small  $I_{on}/I_{off}$  ratio (1.3 for  $V_G$  at ±40 V), and low electron mobility. It is suggested that the weak gate coupling caused by the thick dielectric and the back-gate device configuration is responsible for its poor performance.<sup>4,19</sup>

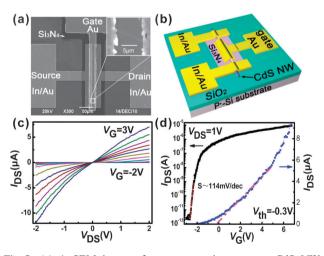

To further improve the device performance, top-gate MISFETs were fabricated based on the CdS: Ga NWs (sample S3) by using high- $\kappa$  Si<sub>3</sub>N<sub>4</sub> ( $\epsilon \sim 7.5$ ) instead of the SiO<sub>2</sub> dielectric. Fig. 5a and b depict the SEM image and the schematic illustration of the device, respectively. Significantly, the top-gate MISFET exhibits a remarkable improvement in the device performance. The device could be switched between the accumulation state and the depletion state within a small gate voltage range from -2 V to +3 V (Fig. 5c). From the transfer characteristics of the device (Fig. 5d), the  $I_{on}/I_{off}$  ratio of the device is as high as  $\sim 10^7$  in the applied gate voltage range. The  $g_m$  value of the device further increases to  $1.07 \ \mu$ S at  $V_{DS} = 1$  V, while the threshold voltage ( $V_{th}$ ) decreases to -0.3 V. The field-effect mobility of the device is estimated to be 241.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> according to the following equation:<sup>19</sup>

$$\mu_{\rm e} = Lg_{\rm m} \ln(1 + 2h/d)/2\pi\epsilon\epsilon_{\rm Si_2N_4} V_{\rm DS} \tag{4}$$

where  $\varepsilon_{\text{Si}_3\text{N}_4}$  is the dielectric constant of Si<sub>3</sub>N<sub>4</sub>. On the other hand, subthreshold swing (S) is also an important parameter for a FET, which is defined as  $S = dV_G/d\log_{10}I_{\text{DS}}$  in the subthreshold region. A small S value is desired to efficiently switch off (on) a FET within a small voltage range. Here, S is

**Fig. 5** (a) A SEM image of a representative top-gate CdS NW MISFET. The inset shows an enlarged SEM image of the FET channel. (b) A schematic illustration of the top-gate CdS NW FET. (c)  $I_{\rm DS}-V_{\rm DS}$  curves measured at varied  $V_{\rm G}$ .  $V_{\rm G}$  increases from -2 to +3 V in steps of +0.5 V. (d) A  $I_{\rm DS}-V_{\rm G}$  curve measured at  $V_{\rm DS} = +1$  V. Both the subthreshold region and the liner part of the  $I_{\rm DS}-V_{\rm G}$  curve were fitted by straight lines to obtain the values of subthreshold swing and transconductance.

deduced to be 114 mV dec<sup>-1</sup> for the top-gate CdS: Ga NW MISFET, in contrast to the much larger value ( $\sim 816 \text{ V dec}^{-1}$ ) for the back-gate FET, and approaches the theoretical value (60 mV dec<sup>-1</sup>) for a FET at room-temperature. Moreover, the electron concentration (n) in the CdS: Ga NW is determined to be 2.6  $\times$  10<sup>17</sup> cm<sup>-3</sup> from the equation  $n = \sigma/e\mu_{\rm e}$ , where  $\sigma$  is the conductivity of the NW at zero gate voltage, and e is the elementary charge. This value is smaller than that obtained from the XPS detection (~1.9 at.%, corresponding to a Ga donor concentration  $> 10^{19} \text{ cm}^{-3}$ ). Since the XPS signal is detected from a large area of NW film, the uneven doping and the existence of a small amount of Ga impurities will result in the large XPS value. On the other hand, this result also indicates that only a small portion of Ga donors could be activated and contribute to the conductivity of the CdS: Ga NWs. It is noted that over ten CdS: Ga NW MISFETs were measured in this work. All of them show stable device performances with mobilities larger than 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and S in the range of 80–150 mV dec<sup>-1</sup>, indicating good reproducibility of the devices.

The substantial improvement in the device performance of the top-gate CdS: Ga NW MISFET could be attributed to the use of the high- $\kappa$  Si<sub>3</sub>N<sub>4</sub> dielectric as well as the top-gate device configuration.<sup>4,5,19</sup> The thin  $Si_3N_4$  insulator leads to a remarkable enhancement in the channel capacitance and thus allows more efficient gate modulation to the conduction channel. This gate modulation is further improved by the surrounding top gate. We also note that nanoFETs fabricated from the undoped CdS NWs (S0) show very poor performances with faint gating effects even when the same top-gate geometry and the high- $\kappa$  dielectric are used (data not shown), indicating that the appropriate channel doping plays an important role in obtaining high-performance nanoFETs. A serious contact problem in nanoFETs fabricated from intrinsic nanostructures usually causes the degeneration of the device performance. By increasing the carrier concentration in the conduction channel, the contact barrier, if it exists, will be much lower and thinner, thus allowing the carriers to pass through the interface via direct electron tuning and resulting in a low contact resistance. Besides the electrode contact, the channel doping also offers the capability to control the threshold voltage, which is important for the practical application of the nanoFETs. However, the highly doped CdS NWs show worse performances, since the NWs become more metallic rather than semiconducting in this case. Therefore, a balance should be taken between the doping concentration and the device performance. In this work, sample S3, which has a modest doping concentration, is found to be most suitable for highperformance device applications.

To demonstrate the promising applications of the n-type CdS:Ga NWs in nano-optoelectronics, nanoLEDs based on the NWs were also constructed, as shown in Fig. 6a. The n-CdS NW/p<sup>+</sup>-Si substrate hybrid p–n junction exhibits excellent rectification behavior with a small turn-on voltage of  $\sim 2.4$  V (Fig. 6b). A bright yellow spot of light could clearly be observed by the naked eye from the optical microscope in the probe station even at a relatively low forward bias of +5 V (inset in Fig. 6b), and the light intensity could be further adjusted by changing the forward voltage.

**Fig. 6** (a) A schematic illustration of the nanoLED fabricated from the n-CdS  $NW/p^+$ -Si substrate heterojunction. (b) The rectifying characteristic of the hybrid p–n junction. The inset shows the yellow spot of light captured by the optical microscopy on the probe station.

#### IV. Conclusions

In summary, Ga-doped CdS NWs were successfully synthesized by using a Ga<sub>2</sub>O<sub>3</sub> and Ga mixed powder as the n-type dopant *via* thermal evaporation. Through adjusting the Ga doping level, the conductivities of the CdS : Ga NWs could be tuned over a wide range of nearly nine orders of magnitude. Highperformance MISFETs based on individual NWs were constructed by using a high- $\kappa$  Si<sub>3</sub>N<sub>4</sub> dielectric and a top-gate device geometry, and showed a substantial improvement in device performance. Moreover, nanoLEDs were obtained by taking advantage of a n-CdS NW/p<sup>+</sup>-Si substrate hybrid device structure. Bright yellow emission from the nanoLED was clearly observed at a relatively low forward voltage. It is expected that the CdS NWs with tunable transport properties have great potential in nanoelectronic and nano-optoelectronic devices.

#### Acknowledgements

This work was supported by financial support from the National Natural Science Foundation of China (Nos. 60806028, 20901021, 50903059), the Program for New Century Excellent Talents in University of the Chinese Ministry of Education (NCET-08-0764), the Major Research Plan of the National Natural Science

Foundation of China (No. 91027021), and the Fundamental Research Funds for the Central Universities.

#### References

- 1 J. S. Jie, W. J. Zhang, I. Bello, C. S. Lee and S. T. Lee, *Nano Today*, 2010, **5**, 313.

- 2 T. Y. Zhai, X. S. Fang, L. Li, Y. Bando and D. Golberg, *Nanoscale*, 2010, **2**, 168.

- 3 J. S. Jie, W. J. Zhang, Y. Jiang and S. T. Lee, *Appl. Phys. Lett.*, 2006, **89**, 223117.

- 4 D. Wu, J. Yang, L. Wang, S. Y. Li, B. Wu, Y. Q. Yu, C. Y. Wu and J. S. Jie, *Appl. Phys. Lett.*, 2010, **96**, 123118.

- 5 P. C. Wu, R. M. Ma, C. Liu, T. Sun, Y. Ye and L. Dai, *J. Mater. Chem.*, 2009, **19**, 2125.

- 6 J. S. Jie, W. J. Zhang, Y. Jiang, X. M. Meng, Y. Q. Li and S. T. Lee, *Nano Lett.*, 2006, 6, 1887.

- 7 C. Y. Wu, J. S. Jie, L. Wang, Y. Q. Yu, Q. Peng, X. W. Zhang, J. J. Cai, H. E. Guo, D. Wu and Y. Jiang, *Nanotechnology*, 2010, 21, 505203.

- 8 T. Y. Wei, C. T. Huang, B. J. Hansen, Y. F. Lin, L. J. Chen, S. Y. Lu and Z. L. Wang, *Appl. Phys. Lett.*, 2010, 96, 013508.

- 9 Z. Y. Fan, J. C. Ho, T. Takahashi, R. Yerushalmi, K. Takei, A. C. Ford, Y. L. Chueh and A. Javey, *Adv. Mater.*, 2009, 21, 3730.

- 10 C. J. Barrelet, A. B. Greytak and C. M. Lieber, *Nano Lett.*, 2004, 4, 1981.

- 11 A. L. Pan, D. Liu, R. B. Liu, F. F. Wang, X. Zhu and B. S. Zou, Small, 2005, 1, 980.

- 12 A. B. Greytak, C. J. Barrelet, Y. Li and C. M. Lieber, *Appl. Phys. Lett.*, 2005, 87, 151103.

- 13 Y. Huang, X. F. Duan and C. M. Lieber, Small, 2005, 1, 142.

- 14 K. Y. Lee, J. R. Lim, H. Rho, Y. J. Choi, K. J. Choi and J. G. Park, *Appl. Phys. Lett.*, 2007, **91**, 201901.

- 15 A. L. Pan, R. B. Liu and B. S. Zou, Appl. Phys. Lett., 2006, 88, 173102.

- 16 R. M. Ma, L. Dai, H. B. Huo, W. Q. Yang and G. G. Qin, *Appl. Phys. Lett.*, 2006, **89**, 203120.

- 17 Z. B. He, J. S. Jie, W. J. Zhang, W. F. Zhang, L. B. Luo, X. Fan, G. D. Yuan, I. Bello and S. T. Lee, *Small*, 2009, 5, 345.

- 18 J. S. Jie, G. Z. Wang, X. H. Han, Q. X. Yu, Y. Liao, G. P. Li and J. G. Hou, *Chem. Phys. Lett.*, 2004, 387, 466.

- 19 Z. B. He, W. J. Zhang, W. F. Zhang, J. S. Jie, L. B. Luo, G. D. Yuan, J. X. Wang, C. M. L. Wu, I. Bello, C. S. Lee and S. T. Lee, *J. Phys. Chem. C*, 2010, **114**, 4663.